O IC 4017 pode ser considerado um dos chips mais úteis e versáteis com inúmeras aplicações em circuitos eletrônicos.

Sobre IC 4017

Tecnicamente, é chamado de divisor de contador de décadas de 10 estágios da Johnsons. O nome sugere duas coisas, é algo a ver com o número 10 e contar/dividir.

O número 10 está conectado com o número de saídas que este IC possui, e essas saídas se tornam altas em sequência em resposta a cada pulso de clock alto aplicado em seu pino de clock de entrada.

Isso significa que todas as suas 10 saídas passarão por um ciclo de sequenciamento de saída alta do início ao fim em resposta a 10 clocks recebidos em sua entrada (pino 14). Então, de certa forma, está contando e também dividindo o clock de entrada por 10 e, portanto, o nome.

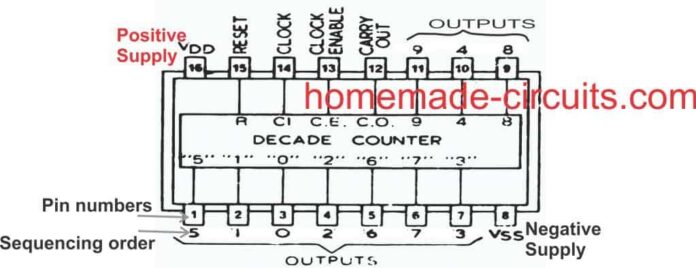

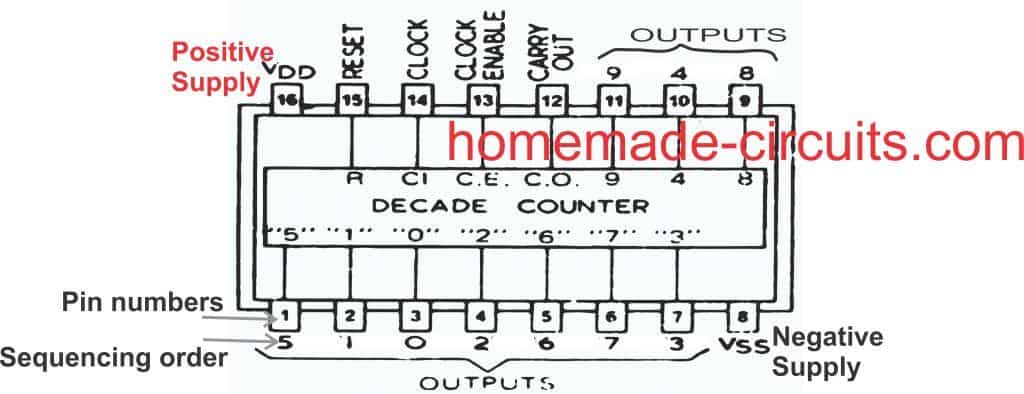

Entendendo a função de pinagem do IC 4017

Vamos entender os pinos do IC 4017 em detalhes e do ponto de vista de um novato: Observando a figura, vemos que o dispositivo é um DIL IC de 16 pinos, os números de pinos são indicados no diagrama com seus nomes de atribuição correspondentes.

O que significa lógica alta, lógica baixa

A pinagem que é marcada como saída são os pinos que são renderizados logicamente “alto” um após o outro em uma sequência em resposta aos sinais de clock no pino 14 do IC.

“Lógica alta” significa simplesmente atingir um valor de tensão de alimentação positivo, enquanto “lógica baixa” refere-se a atingir o valor de tensão zero.

Quando o IC 4017 é inicialmente ligado, ele é reinicializado e uma lógica alta aparece no pino 3 por padrão. Discutiremos o processo de redefinição nos parágrafos posteriores.

Nesta posição, quando o primeiro pulso de clock é aplicado no pino #14, a lógica existente no pino #3 salta do pino #3 para a próxima pinagem que é o pino #2. A lógica alta permanece travada no pino #2 até que o próximo clock seja aplicado no pino #14, o que faz com que a lógica alta no pino #2 salte do pino #2 para a próxima pinagem de saída que é o pino #4, e esse sequenciamento de A lógica alta continua até atingir a última pinagem do IC que é o pino 11, após o qual a sequência lógica alta volta para o pino 3 e o ciclo se repete novamente.

Qual é a ordem de sequenciamento do pino de saída?

Para ser mais preciso, o movimento de sequenciamento acontece através das pinagens: 3, 2, 4, 7, 10, 1, 5, 6, 9, 11…

Após o pino 11, o IC reinicializa internamente e reverte a lógica alta no pino 3 para repetir o ciclo.

Por que o pino 15 deve ser aterrado

Este sequenciamento e reinicialização são realizados com sucesso apenas enquanto o pino 15 estiver aterrado ou mantido em um nível lógico baixo, caso contrário, o IC pode funcionar mal. Se for mantido alto, o sequenciamento não acontecerá e a lógica no pino 3 permanecerá travada.

Observe que a palavra “alta” significa uma tensão positiva que pode ser igual à tensão de alimentação do IC, então quando digo que as saídas se tornam altas de maneira sequencial significa que as saídas produzem uma tensão positiva que muda de maneira sequencial de um pino de saída para o próximo, de uma maneira DOT “em execução”.

O pino 14 precisa de frequência externa (sinal de relógio)

Agora, o sequenciamento ou deslocamento da lógica de saída explicado acima de um pino de saída para a próxima saída pode ser executado apenas quando um sinal de clock é aplicado à entrada de clock do IC que é o pino #14.

Lembre-se, se nenhum relógio for aplicado a esta entrada pino 14, ela deve ser atribuída a uma alimentação positiva ou negativa, mas nunca deve ser mantida suspensa ou desconectada, conforme as regras padrão para todas as entradas CMOS.

O pino de entrada de clock #14 responde apenas a clocks positivos ou a um sinal positivo (borda ascendente), e a cada sinal de pico positivo consequente, a saída do IC muda ou se torna alta em sequência, o sequenciamento das saídas é da ordem de pinagem #3, 2, 4, 7, 10, 1, 5, 6, 9, 11.

O pino 13 é oposto ao pino 14

O pino 13 pode ser considerado o oposto do pino 14 e este pino responderá a sinais de pico negativos. Ou seja, se um clock negativo for aplicado a este pino, também produzirá a mudança de “lógica alta” nos pinos de saída

No entanto, normalmente esta saída de pinos nunca é usada para aplicar os sinais de clock, em vez disso, o pino #14 é usado como a entrada de clock padrão.

Portanto, o pino 13 precisa ser atribuído a um potencial de terra, ou seja, deve ser conectado ao terra para permitir que o IC funcione.

Caso o pino #13 esteja conectado ao positivo, todo o IC irá parar e as saídas irão parar de seqüenciar e parar de responder a qualquer sinal de clock aplicado no pino #14.

Como o pino 15 funciona como redefinir o pino

O pino 15 do IC é a entrada do pino de reset. A função deste pino é reverter a sequência de volta ao estado inicial em resposta a um potencial positivo ou tensão de alimentação.

Ou seja, quando uma tensão positiva momentânea atinge o pino 15, a sequência lógica de saída volta ao pino 3 e inicia o ciclo novamente.

Se a alimentação positiva for mantida conectada a este pino #15, novamente paralisa a saída do sequenciamento e a saída se prende ao pino #3, tornando esta pinagem alta e fixa.

Portanto, para fazer o IC funcionar, o pino #15 deve sempre ser conectado ao terra.

Se esta pinagem se destina a ser usada como uma entrada de resetentão ele pode ser aterrado com um resistor em série de 100K ou qualquer outro valor alto, de modo que uma alimentação positiva externa agora possa ser introduzida livremente nele, sempre que o IC precisar ser reinicializado.

Usando o pino 15 para reduzir o número de sequência de saída

Como aprendemos acima, existem 10 saídas na ordem de pinagem de 3, 2, 4, 7, 10, 1, 5, 6, 9, 11.

O sequenciamento começa no pino 3 e termina no pino 11, onde o IC é reiniciado e a sequência reverte para o pino 3 para iniciar um novo ciclo.

No entanto, suponha que você não queira usar todas as 10 sequências de saída, em vez disso, queira limitar a sequência a apenas 5 números. Ou seja, você deseja usar o sequenciamento de saída na ordem de 3, 2, 4, 7, 10. A sequência deve começar no pino 3 e terminar no pino 10 e retornar ao pino 3.

No entanto, isso não pode acontecer enquanto o pino 15 estiver conectado ao terra. Para limitar o sequenciamento a uma contagem mais baixa desejada, o pino 15 deve ser desconectado da linha de aterramento e conectado ao pino de saída que vem logo após a pinagem da última sequência.

No exemplo acima, onde queremos que a sequência termine no pino 10, a próxima pinagem que vem depois do pino 10 é o pino 1, então o pino 15 deve ser conectado a este pino 1, para garantir que sempre que o sequenciamento atinge o pino 1, ele é instantaneamente revertido para o pino 3 para um novo ciclo e o sequenciamento máximo de saída é limitado a apenas 5 contagens.

Da maneira acima, você pode limitar o sequenciamento de saída para qualquer outra contagem desejada abaixo de 10.

Pino de aterramento e pino de execução

O pino #8 é o pino terra e deve ser conectado ao negativo da alimentação, enquanto o pino #16 é o positivo e deve ser terminado no positivo da alimentação de tensão.

O pino 12 é a execução e é irrelevante, a menos que muitos ICs estejam conectados em série, discutiremos isso outro dia. O pino 12 pode ser deixado aberto.

Tem dúvidas específicas?? sinta-se à vontade para perguntar a eles através de seus comentários… todos serão cuidadosamente abordados por mim.

Diagrama de conexão de pinagem básica IC 4017

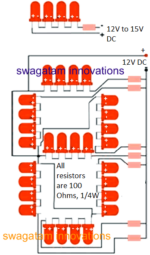

Circuito de perseguição de LED de aplicação usando IC 4017 e IC555

O exemplo de circuito GIF a seguir mostra como a pinagem de um IC 4017 geralmente é conectada a um oscilador para obter as saídas altas da lógica sequencial. Aqui as saídas são conectadas a LEDs para indicar o deslocamento sequencial das lógicas em resposta a cada pulso de clock gerado pelo oscilador IC 555 no pino 14 do IC 4017.

Você pode ver que a mudança lógica acontece em resposta apenas ao clock positivo ou borda positiva no pino 14 do IC 4017. A sequência não responde aos pulsos ou clocks negativos.

Simulação de Trabalho IC 4017

Videoclipe:

Como conectar dois ICs 4017 em cascata para obter 17 saídas de sequenciamento

O diagrama acima mostra como conectar dois 4017s juntos para criar um contador/decodificador de 10 a 17 estágios. Ele mostra como cascatear dois ICs 4017 para obter 17 saídas de sequenciamento em vez de apenas 10 de um único IC. O circuito é mostrado configurado para dividir por 17.

O sinal de clock é fornecido em paralelo ao IC1 e IC2. Assim que a contagem cai abaixo de 9, a saída ‘9’ do IC1 fica baixa, fazendo com que o pino de inibição do clock do IC2 seja definido como alto através do IC3c, evitando que o IC2 seja impactado pelos sinais do clock.

A saída ‘9’ de IC1 sobe alto quando o 9º pulso de clock chega, inibindo IC1 de mais ação de clock, enquanto simultaneamente conduz o terminal de inibição de clock de IC2 para baixo através de IC2c, permitindo que IC2 responda a mais sinais de clock.

Quando o 17º pulso de clock chega, a saída ‘9’ do IC2 oscila alto por um breve período, acionando o monoestável IC3a -IC3b 15uS. Este pulso de 15us redefine ambos os contadores para os estados vazio ou ‘0’.

Depois disso, a sequência de contagem recomeça sozinha. Como a saída ‘9’ do IC1 e as saídas ‘0’ e ‘9’ do IC2 são “perdidas” no processo de contagem, o circuito tem apenas 17 estágios de contador/decodificador disponíveis. Ao conectar o pino de entrada “livre” do IC2a ao pino de saída correspondente do IC2, o circuito pode ser contado por qualquer número entre 10 e 17.

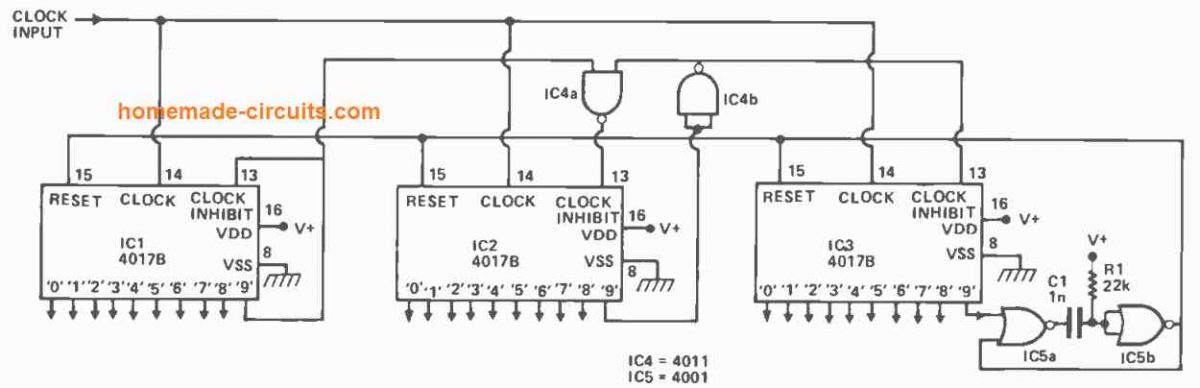

Como conectar três IC 4017 em cascata para obter 25 saídas de sequenciamento

A configuração para criar um contador/decodificador de 18 a 25 estágios a partir de três 4017s pode ser vista no diagrama acima. IC3 é inibido pelo IC4b e pela saída baixa ‘9’ do IC2, enquanto o IC2 é inibido pelo IC4a e pela saída baixa ‘9’ do IC1, até o 9º pulso de clock. Entre o 10º e o 17º pulso de clock, IC1 é inibido por sua saída ‘9’ alta, enquanto IC3 é inibido por IC4b e a saída ‘9’ baixa de IC2.

Subsequentemente, entre o 18º e o 25º pulsos de clock, IC1 é inibido por sua saída ‘9’ alta, e IC2 é inibido através das saídas ‘9’ altas de IC1 e IC2 usando IC4c, e todo o circuito é redefinido para o ‘0’ estado por meio do monoestável IC5a e IC5b.

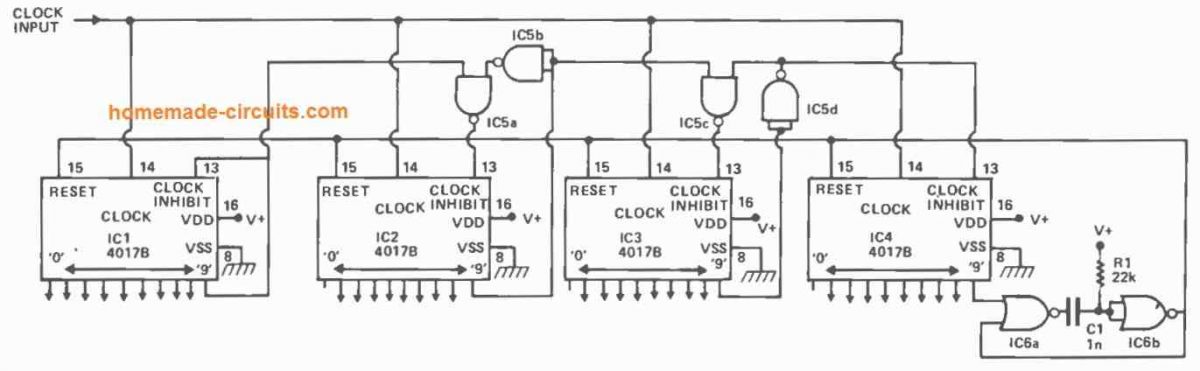

Como conectar quatro IC 4017 em cascata para obter 33 saídas de sequenciamento

Usando uma operação de divisão por 33, a configuração acima mostra como fazer um conjunto de contador/decodificador de 26 a 33 estágios. Ao interpor estágios extras de IC2-1C5a-1C5b entre 1C2 e 1C3, esse design pode ser estendido para fornecer um número qualquer de estágios de saída decodificados. Cada estágio 40178 subsequente adiciona oito saídas decodificadas ao sistema.

Hashtags: #Como #entender #pinagens

FONTE

Nota: Este conteúdo foi traduzido do Inglês para português (auto)

Pode conter erros de tradução

Olá, se tiver algum erro de tradução (AUTO), falta de link para download etc…

Veja na FONTE até ser revisado o conteúdo.

Status (Ok Até agora)

Se tiver algum erro coloque nos comentários